基于自己的IP可以搭建一揽子的计算机互联体系方案,也是为AI应用助力,奎芯把这些方案统称为M2LINK。

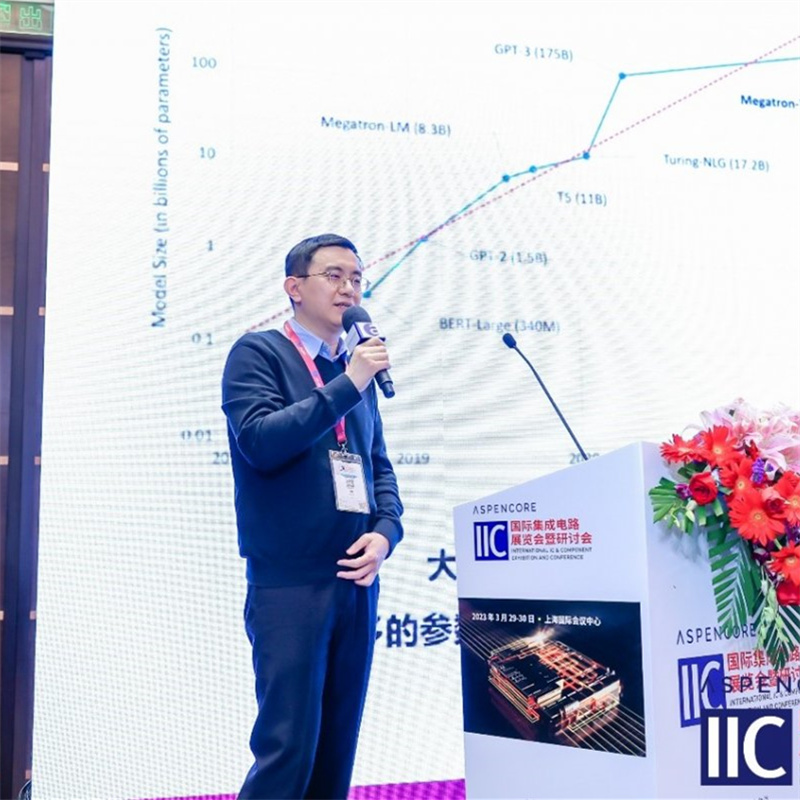

3月29日,由全球领先的技术媒体机构AspenCore主办的2023国际集成电路展览会暨研讨会(IIC Shanghai 2023)同期的EDA/IP与IC设计论坛,邀请了包括Cadence、芯瑞微、Andes、奎芯科技、芯和半导体、思尔芯、 安谋等多家来自EDA工具、IP解决方案等厂商代表作了相关深度分享。其中,奎芯科技 市场及战略副总裁 唐睿作了主题为“奎芯M2Link Chiplet D2D 赋能高性能计算”的演讲,分享内容涉及ChatGPT所引发的算力需求暴增,Chiplet的产业发展,UCIe标准以及奎芯的M2Link。

奎芯科技 市场及战略副总裁 唐睿

奎芯科技 市场及战略副总裁 唐睿

ChatGPT引发算力需求的暴增

Chiplet是近来科技领域最火爆的话题,基本上影响了大家的生活和工作。

唐睿指出,从训练和推演的角度来看,ChatGPT是需要巨大的算力去支撑的,GPT3需要1750亿个模型参数,GPT3.5和GPT4模型参数规模和GPT3是不相上下的,像微软和英伟达推的模型参数已经达到了五千亿之多。

从2008年到2021年,自然模型参数几乎每年提升一个数量级,增量非常厉害,所以在算力角度的需求很大,微软的数据中心搭建了一个超过四千个CPU、一千个GPU的计算集群,去为OpenAI训练ChatGPT的模型。推演的时候,支持目前OpenAI的推演需求和客户支持的需求,是需要三千多台A100的服务器,约等于近三万个GPU。最新的DGX H100,主要的CPU拓展都依赖于高速互联的slution。计算体系是依托互联进行拓展,计算体系互联从内到外带宽是逐级递减,但延迟也是逐级递增的,可以看到片内封装级互联以及芯片互联是落在狭义的Chiplet领域。

Chiplet的产业发展

回顾Chiplet的产业发展我,他认为Chiplet是大算力时代的唯一选择,究其原因主要涉及四点:成本、性能、生态和市场。

从成本端看,它是比较小的尺寸,良率会更高,也可以用不同的制程去进行组合,所以成本上具有优势。

从性能的角度,后摩尔时代算力进一步扩展,只能依靠Chiplet去做。

从芯片开发角度来看,Chiplet给芯片的架构师带来了一些新的挑战——如何把原来的在一个单代上的ICOC集成到小的Chiplet上做合理的规划和拆解,对架构是极大的挑战,如果进展顺利,是可以改变整个芯片设计的生态,也可以大大降低芯片开发的门槛,缩短芯片上市的时间。

从应用端来看,其实Chiplet也增加了IP硬件的复用性,也针对不同的底层应用做不同的Chiplet拼接调整,也可以增加芯片定制化的趋势。

UCIe标准及M2Link

由于Chiplet 产品形态多样,标准各异,2022年8月科技巨头们积极布局Chiplet并推出相关产品,共同成立了Chiplet标准联盟,正式推出了通用Chiplet的高速互联标准“UCIe”。

唐睿表示,UCIe是定义了Data和Clk是如何互联的,它是并角比较少,做一个并行对电流转换,就带来了较多的延迟和功耗,目前还是比较适合传统的封装形式。另一种就是类比ER的并行机构,除了Data以外,还要传Rwded,因为线路比较多,所以整体的带宽并不低,它带来的一个问题就是因为本身并角较多,其整体架构还是比较轻量级的,因为没有并行到串行的转换,功耗和延迟也会相对低很多。因为需要同步传输很多信号,所以说缺点也很明显,只能适合相对距离比较近,间距比较小的应用场合,一般也比较适合先进封装去采用。

UCIe是目前主流CPU公司做推广的Chiplet并行互联标准。UCIe的层级定义比较完备,包括从物理层到适配层再到协议层,它的功耗和延迟也是要求比较高的,而且UCIe本身是针对不同的封装,它定了一些非常关键的指标,像速率、线宽、线距、封装形式、带宽密度、功耗延迟等等。目前,UCIe有如下几个应用场景,首先是计算代到memory,第二种是C2C,就是两个计算小芯片互联,还有C2 I/O,还有C2O,就是计算小芯片和其他小芯片互联。

除了物理层和协议层之外,UCIe还定义了中间层,由于中间层定义非常关键的,需要实现多种协议的仲裁,也将一些纠错、重传机制、功能也放进来,最上层协议层支持PCAE等等协议。

在片间互联方面,该厂商也有自己的C2C方案和C2M模组方案,C2C方案兼容PCIE CXL的国际标准协议,是相对比较短距的芯片互联。除了提供Chiplet IP和产品之外,该厂商还可通过自身强大的供应链资源和系统整合能力,为客户打造一站式的Chiplet解决方案。

唐睿介绍道,奎芯可以提供整个计算体系,尤其是节点内的统一的互联方案--M2Link。从产品的角度来看,奎芯核心的M2LINK D2D分成两代产品,第一代是支持2D的封装,目前在12纳米功率上做的,预计是今年第四季度面市。第二代是支持2.5D的先进封装,会在更先进的工艺,像台积的6纳米工艺上进行IP的研发,单个速率可以达到32G DPS,之前有64个位,再加上四个模组,所以整体带宽可以到4G。

扩展开来看,基于自己的IP可以搭建一揽子的计算机互联体系方案,也是为AI应用助力,奎芯把这些方案统称为M2LINK,除了前面介绍的D2D之外,该厂商还有D2M,主要支持像目前最新的HBM3的协议,以及国内未来可能有的内存标准协议。此外,除提供Chiplet IP和产品之外,该厂商还可通过自身强大的供应链资源和系统整合能力,为客户打造一站式的Chiplet解决方案。

川公网安备51010802032667号

川公网安备51010802032667号